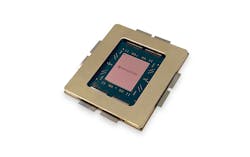

Broadcom intros ‘Bailly,’ a co-packaged optics networking switch

Laser Focus World: What inspired this work?

Rajiv Pancholy: There were two main inspirations: The first is a disruption to optical interconnects’ cost, power, and reliability for critical networking applications. The second is migrations of critical workloads into the cloud and the introduction of new services processing large amounts of data. These trends are driving a need for purpose-built artificial intelligence (AI) and machine learning (ML) fabrics that will require new scale-up and scale-out compute and networking architectures.

LFW: How does Bailly work and what kinds of benefits does it provide?

Pancholy: Today, network switching is done inside hyperscale data centers with a switch ASIC (application-specific integrated circuit). Each of these ASICs is connected to pluggable optical receivers to connect layers (LEAF, SPINE, etc.) to transmit data. These traditional switch systems with pluggable or socketed optical transceivers require high power to equalize signal impairments incurred on a signal as it traverses long traces and through multiple connector discontinuities. Escape density is constrained in traditional systems by the mechanical design limits of transceiver electrical connectors. By eliminating these interfaces and driving the optics directly from the switch ASIC, we can provide a 30% system power reduction and significantly reduce the cost/bit.

LFW: Most surprising thing about Bailly?

Pancholy: It’s an all-optical 51.2-T CPO switch that can achieve 5.5 W of power per 800 G. Currently available pluggable modules require 14–16 W/800 G.

LFW: Why silicon photonics?

Pancholy: Silicon photonics provides a way to integrate package photonics and electronics. With it, we can collapse 128 optical transceivers—at least three cubic feet in volume—down to the size of four quarters. And through this collapse, we save 50% on I/O power.

Juniper, Cisco, Marvell, and many others have made acquisitions to get into silicon photonics. Intel and now Broadcom have developed the technology in-house with deep investments.

LFW: Applications?

Pancholy: As we start to demonstrate full functionality of the highest-density photonics ICs, we’ll facilitate beachfront connectivity challenges on single reticle ASICs while lowering the total cost/bit. CPO will enable not only networking, but GPU-to-GPU (graphical processing unit) interconnects, resource pooling, and memory disaggregation while we continue to address the needs of AI/ML training clusters with high-bandwidth, radix connectivity, and the lowest cost per bit with the lowest power usage effectiveness.